#### Architetture dei Calcolatori

#### Reti Sequenziali

Prof. Francesco Lo Presti

#### Rete Sequenziale

#### Circuiti Sequenziali

- ☐ Si introduce il concetto di stato

- □ I valori in uscita influenzano gli ingressi (feedback)

- □ Asincroni: il cambio di stato di un elemento influenza immediatamente gli ingressi del circuito

- □ Sincroni: il cambio di stato di uno o più elementi influenza gli ingressi del circuito solo in istanti predeterminati, uquali per tutti

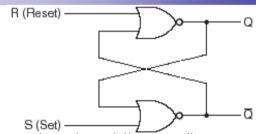

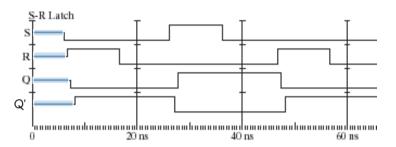

#### Latch SR

- ☐ Gli ingressi dipendono dalle uscite!!

- □ È un elemento di memoria

- o Memorizza 1 bit

- □ Q è il bit memorizzato nel latch SR

- ☐ Ha due stati:

2

- o set: Q=1 ( $\overline{Q}$ =0)

- $\circ$  reset: Q=0 ( $\overline{Q}$ =1)

- □ Gli ingressi S e R possono essere utilizzati per cambiare lo stato del latch

#### Latch SR

Prossimo Stato in funzione degli ingressi e dello stato corrente

| S | R | Q(k) | Q(k+1) |   |                    |

|---|---|------|--------|---|--------------------|

| 0 | 0 | 0    | 0      | 1 | reset (stabile)    |

| 0 | 0 | 1    | 1      | 0 | set (stabile)      |

| 0 | 1 | 0    | 0      | 1 | reset (stabile)    |

| 0 | 1 | 1    | 0      | 1 | reset (transiente) |

| 1 | 0 | 0    | 1      | 0 | Set (transiente)   |

| 1 | 0 | 1    | 1      | 0 | Set (stabile)      |

| 1 | 1 | 0    | 0      | 0 | <i>!!</i>          |

| 1 | 1 | 1    | 0      | 0 | <i>!!</i>          |

1

#### Fyitare S=R=1...

- Quando entrambi gli ingressi commutano da 1 a 0 avviene una race condition

- □ Entambe le uscite vengono portate da 0 a 1

- □ A causa delle differenze anche minime tra due NOR gates i tempi di commutazione possono differire tra loro -> uno delle due uscite commuta prima dell'altra

- La commutazione della prima porta impedisce la commutazione dell'altra

- □ Conclusione: il valore di uscita non è predicibile

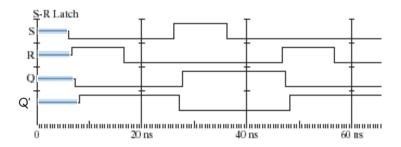

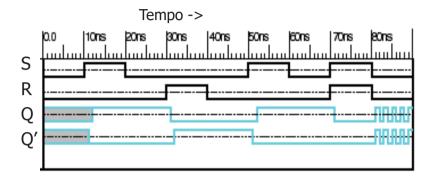

#### Comportamento di un Latch SR nel tempo

5

#### Evitare S=R=1...

- Quando entrambi gli ingressi commutano da 1 a 0 avviene una race condition

- □ Entambe le uscite vengono portate da 0 a 1

- □ Entrambe le porte NOR commutano nello stesso instante

- $\circ$  Questo comporta la commutazione delle uscite da 0 a 1

- ...che a sua volta comporta la commutazione delle uscite da 1 a 0

- $\circ$  ...che a loro volta faranno commutare nuovamente le uscite da  $\circ$  a  $\circ$

- o ...etc. etc. etc.

- □ Conclusione: le uscite oscilleranno tra 0 e 1!

6

,

| S | R | Q <sub>n+1</sub> |

|---|---|------------------|

| 0 | 0 | Q <sub>n</sub>   |

| 0 | 1 | 0                |

| 1 | 0 | 1                |

| 1 | 1 |                  |

0

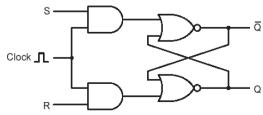

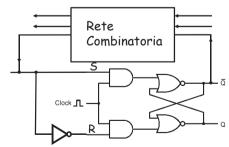

#### Aggiungiamo un segnale di clock al latch SR

□ Un segnale di clock è usato per assicurarsi che il latch possa commutare solo in determinati momenti

Segnale di clock

□ Il latch reagisce ai valori di S e R solo quando il clock è pari a 1

## Il ruolo del segnale di clock

- □ Il segnale di clock assicura che le modifiche agli ingressi si propaghino alle uscite solo quando richiesto

- □ Clock di Sistema: segnare periodico di periodo T e frequenza f=1/T

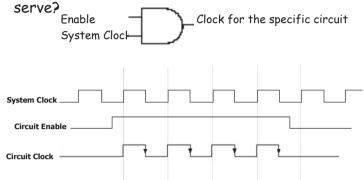

#### Clock di un circuito a partire dal clock di sistema

□ Il clock di Sistema commuta ogni ciclo: come si può contrallare un particolare circuito solo quando

12

#### ...di consequenza...

□ Nel caso di commutazione da (S=1,R=0) a (S=0,R=1) o da (S=0,R=1) a (S=1,R=0) le uscite del latch SR per un piccolo intervalló tempo potrebbero trovarsi nello stato dove entrambe le uscite sono 0

|   | Stato<br>inizial<br>e | Cambio ingresso | Stato<br>Transiente | Stato<br>Stabile |  |  |

|---|-----------------------|-----------------|---------------------|------------------|--|--|

| S | 1                     | 0               | 0                   | 0                |  |  |

| R | 0                     | 1               | 1                   | 1                |  |  |

| Q | 1                     | 1               | 0                   | 0                |  |  |

| Q | 0                     | 0               | 0                   | 1                |  |  |

$\square$  Se Q e  $\overline{\mathbb{Q}}$  sono ingressi ad un circuito, quest'ultimo riceve ingressi con valori errati (per un certo intervallo di tempo) causando uscite con valori errati (sempre per un certo intervallo di tempo)

## Un problema sottile...

□ Con il clock=1, le uscite del latch continuano a cambiare ogni qual volta cambiano gli ingressi

...una consequenza...

Consideriamo il sequence circuito

Quando C=1, il valore di Q può continuare ad cambiare O Quante volte?

Desiderato: Il valore di Q deve cambiare (al più) una ed una sola volta durante uns

ciclo di clock

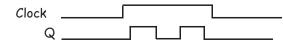

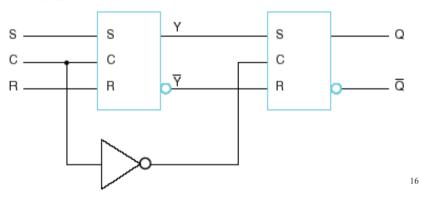

# Soluzione: Circuito Flip-Flop master slave

- □ Due latch SR (master e slave)

- O Il master (collegato agli ingressi del circuito) può cambiare il suo stato solo quando il suo stato guando il Clock=1

- Lo slave (collegato alle uscite) cambia il suo stato quando il clock=0

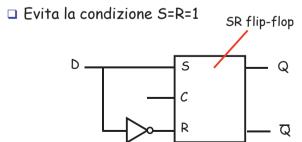

#### Flip Flop D (Delay)

- ☐ Un unico ingrresso D

- $\circ R = \overline{5}$

# Soluzione: Circuito Flip-Flop master slave

- □ Due latch SR (master e slave)

- Il master (collegato agli ingressi del circuito) può cambiare il suo stato solo quando il suo stato quando il Clock=1

- Lo slave (collegato alle uscite) cambia il suo stato quando il clock=0

- □ Pertanto:

- Lo slave legge in ingresso l'output del master solo dopo che questo si è stabilizzato (clock=0)

- Un eventuale circuito a valle riceve in ingresso i valori in uscita dello slave quando le uscite saranno stabilizzate (clock=1)

- Questo permette di controllare quando l'uscita di un circuito a monte impatta gli ingressi del circuito a valle

17

#### Flip Flop D (Delay)

- □ Il flip-flop D rappresenta una cella di memoria

- Memorizza (e rende disponibile in uscita il valore presentato in ingresso

Simbolo

Tabella di Verità

$$\begin{array}{c|c} D & Q_{n+1} \\ \hline 0 & 0 \\ \hline 1 & 1 \\ \end{array}$$

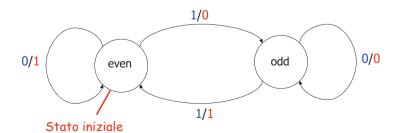

#### Automa a Stati Finiti (ASF) Finite State Machine (FSM)

- □ Modello Formale per descrivere un circuito sequenziale

- □ Descritto tramite una tabella di transizioni tra stati in funzione degli ingressi

- 🗖 e una tabella di uscite in funzione degli ingressi e/o stato

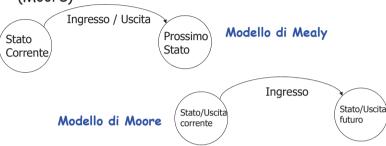

- □ Due Modelli formali:

- O Modello di Moore: uscite sono funzione solo dello stato

- O Modello di Mealy: uscite sono funzione dello stato e degli ingressi

20

22

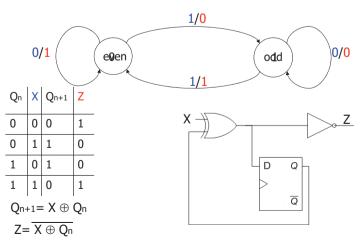

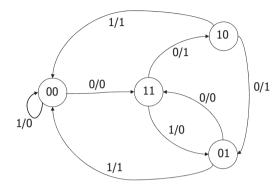

#### Esempio

□ ASF con ingresso binario x, e uscita binaria z. L'uscita è z=1 se e solo se il numero di 1 nella sequenza in ingresso è pari, 0 altrimenti

#### Rappresentazione Grafica

□ Stati sono rappresentate da nodi, transizioni da archi orientate tra stati, ingressi da etichette degli archi, le uscite da etichette degli archi (Mealy) o stati (Moore)

#### Descrizione tabellare dell'ASF

Stato Corrente

odd

| Prossimo state |

|----------------|

| in funzione    |

| dello stato    |

| corrente e     |

| dell'ingresso  |

| Uscita in      |

|----------------|

| funzione dello |

| stato corrente |

| e dell'ingreso |

|                |

| 0                     | even              | 0             | even                |  |  |

|-----------------------|-------------------|---------------|---------------------|--|--|

| 2                     | even              | 1             | odd                 |  |  |

| SO                    | odd               | 0             | odd                 |  |  |

|                       | odd               | 1             | even                |  |  |

|                       |                   |               |                     |  |  |

| dello                 | Stato<br>Corrente | Ingresso      | Prossimo Stato      |  |  |

| dello<br>rente        |                   | Ingresso 0    | Prossimo Stato      |  |  |

| dello<br>rente<br>eso | Corrente          | Ingresso  0 1 | Prossimo Stato  1 0 |  |  |

**Ingresso**

**Prossimo Stato**

1

#### Processo di Astrazione

- ☐ ASF descrive una rete sequenziale (RS)

- □ RS implementa un Automa a Stati Finiti

- L'analisi di una RS permette di risalire al corrispondente ASF

- □ La RS che implementa un dato ASF si ottiene tramite il processo di sintesi

- □ Simile a quanto fatto con funzioni booleane e circuiti combinatori

- O Una Funzione Booleana descrive una rete combinatoria

- O Una Rete Combinatoria implementa una Funzione Booleana

24

26

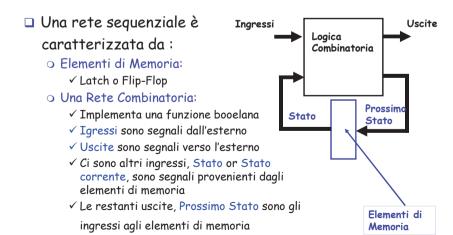

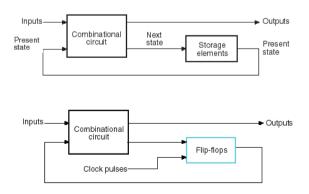

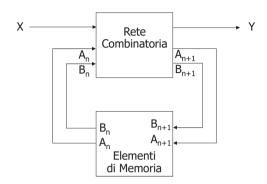

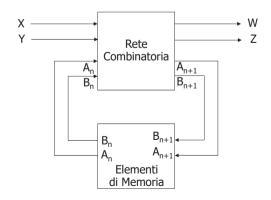

#### Schema di una Rete Sequenziale

#### Sintesi di una Rete Sequenziale

- □ Identificare ingressi, uscite e lo stato

- O Quanti Flip Flop sono necessari?

- O Per un ASF con n stati sono necessari k FFs con  $2^k \ge n$

- O Etichetta ogni stato con una stringa di k bit

- □ Identificare le tabella di verità per le uscite in funzione dello stato e degli ingressi e sintetizzare la relativa rete combinatoria

- ☐ Identificare le tabella di verità corrispondente alla tabella di transizione (prossimo stato in funzione dello stato e degli ingress) e sintetizzare la relativa rete combinatoria

- Determinare la tipologia di Flip Flop per memorizzare lo stato

- O Flip Flop tipo D sono la scelta più semplice

25

#### Esempio

## Esempio 1

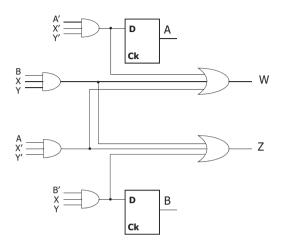

## Esempio 1: Schema Rete

29

28

## Example 1: Tabelle di Transizione

| $A_n$ | B <sub>n</sub> | Х | Υ | A <sub>n+1</sub> | B <sub>n+1</sub> |

|-------|----------------|---|---|------------------|------------------|

| 0     | 0              | 0 | 0 | 1                | 1                |

| 0     | 0              | 1 | 0 | 0                | 0                |

| 0     | 1              | 0 | 0 | 1                | 1                |

| 0     | 1              | 1 | 1 | 0                | 0                |

| 1     | 0              | 0 | 1 | 0                | 1                |

| 1     | 0              | 1 | 1 | 0                | 0                |

| 1     | 1              | 0 | 1 | 1                | 0                |

| 1     | 1              | 1 | 0 | 0                | 1                |

## Esempio 1: Minimizzazione

| Variabili di Stato |    |   |   |  |                  |    |   |   |  |    | Uscita |   |   |  |

|--------------------|----|---|---|--|------------------|----|---|---|--|----|--------|---|---|--|

| A <sub>n+1</sub>   |    | Х |   |  | B <sub>n+1</sub> |    | Х |   |  | Υ  |        | X |   |  |

|                    |    | 0 | 1 |  |                  |    | 0 | 1 |  |    |        | 0 | 1 |  |

| AB                 | 11 | 1 | 0 |  | AB               | 11 | 0 | 1 |  | AB | 00     | 0 | 0 |  |

|                    | 01 | 1 | 0 |  |                  | 01 | 1 | 0 |  |    | 01     | 0 | 1 |  |

|                    | 00 | 1 | 0 |  |                  | 00 | 1 | 0 |  |    | 11     | 1 | 0 |  |

|                    | 10 | 0 | 0 |  |                  | 10 | 1 | 0 |  |    | 10     | 1 | 1 |  |

## Esempio 1: circuito logico

32

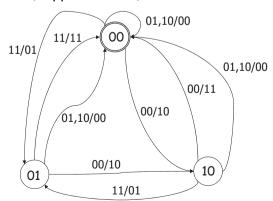

#### Esempio 2: Automa a Stati Finiti

#### □ Stato iniziale (doppio cerchio)

## Esempio 2

#### □ Rete sequenziale con due ingressi

#### □ L'uscita è:

- o 10 quando il numero di ingressi consecutivi 00 è dispari

- O 01 quando il numero di ingressi consecutivi 11 è dispari

- o 11 quando il numero di ingressi consecutivi 00 o 11 è pari

- o 00 altrimenti

#### ■ Esempio:

| INPUT  | 01 | 01 | 00 | 00 | 00 | 11 | 11 | 10 | 11 | 11 | 11 | 11 |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|

| OUTPUT | 00 | 00 | 10 | 11 | 10 | 01 | 11 | 00 | 01 | 11 | 01 | 11 |

#### Esempio 2: Schema Rete Sequenziale

## Esempio 2: tabella di transizione

| $A_n$ | B <sub>n</sub> | Х | Υ | W | Z | A <sub>n+1</sub> | B <sub>n+1</sub> |                     |

|-------|----------------|---|---|---|---|------------------|------------------|---------------------|

| 0     | 0              | 0 | 0 | 1 | 0 | 1                | 0                |                     |

| 0     | 0              | 0 | 1 | 0 | 0 | 0                | 0                |                     |

| 0     | 0              | 1 | 0 | 0 | 0 | 0                | 0                |                     |

| 0     | 0              | 1 | 1 | 0 | 1 | 0                | 1                | Non specificiati in |

| 0     | 1              | 0 | 0 | 1 | 0 | 1                | 0                | quanto lo stato 11  |

| 0     | 1              | 0 | 1 | 0 | 0 | 0                | 0                | non è presente      |

| 0     | 1              | 1 | 0 | 0 | 0 | 0                | 0                | с р. сосс           |

| 0     | 1              | 1 | 1 | 1 | 1 | 0                | 0                |                     |

| 1     | 0              | 0 | 0 | 1 | 1 | 0                | 0                |                     |

| 1     | 0              | 0 | 1 | 0 | 0 | 0                | 0                |                     |

| 1     | 0              | 1 | 0 | 0 | 0 | 0                | 0                |                     |

| 1     | 0              | 1 | 1 | 0 | 1 | 0                | 1                |                     |

| 1     | 1              | 0 | 0 |   |   |                  |                  | )                   |

| 1     | 1              | 0 | 1 |   |   |                  |                  |                     |

| 1     | 1              | 1 | 0 |   |   |                  |                  |                     |

| 1     | 1              | 1 | 1 |   |   |                  |                  | 36                  |

| -     | 1 -            | 1 | - |   |   | l                |                  | 36                  |

## Esempio 2: circuito logico